# LETTER Open Access

# Optimization of deep reactive ion etching for microscale silicon hole arrays with high aspect ratio

Taeyeong Kim<sup>1,2</sup> and Jungchul Lee<sup>1,2\*</sup>

#### **Abstract**

During deep reactive ion etching (DRIE), microscale etch masks with small opening such as trenches or holes suffer from limited aspect ratio because diffusion of reactive ions and free radicals become progressively difficult as the number of DRIE cycle increases. For this reason, high aspect ratio structures of microscale trenches or holes are not readily available with standard DRIE recipes and microscale holes are more problematic than trenches due to omnidirectional confinement. In this letter, we propose an optimization for fabrication of high aspect ratio microscale hole arrays with an improved cross-sectional etch profile. Bias voltage and inductively coupled plasma power are considered as optimization parameters to promote the bottom etching of the high aspect ratio hole array. In addition, flow rates of octafluorocyclobutane ( $C_4F_8$ ) and sulfur hexafluoride ( $SF_6$ ) for passivation and depassivation steps, respectively, are considered as optimization parameters to reduce the etch undercut. As a result of optimization, the aspect ratio of 20 is achieved for 1.3  $\mu$ m-diameter hole array and etch area reduction at the bottom relative to the top is improved to 21%.

Keywords: Deep reactive ion etching, Optimization, High aspect ratio hole array, Silicon

#### Introduction

With the advantage of being able to fabricate high aspect ratio anisotropic patterns on silicon wafers [1, 2], the deep reactive ion etching (DRIE) process has been extensively utilized for many applications including vias for 3D packaging [3, 4] and microelectromechanical systems (MEMS) actuators [5, 6] to name a few. Towards further miniaturization, high-density integration, and higher production yields, DRIE has been routinely adopted for realizing microscale trench and hole arrays with high aspect ratio [7]. However, microscale patterns have suffered from limited etch depth (or aspect ratio) in the Bosch process [8], popular over the cryogenic process [9], because reactive ions and gases cannot effectively diffuse

into the confined etched area as the number of etch cycle increases

To address this problem, researches have been carried out to improve the profile and increase the etch depth by optimizing parameters of the DRIE process for the microscale patterns [7, 8, 10]. Most of the former researches have focused on the fabrication of microscale trenches for X-ray phase contrast imaging [7, 11, 12] and MEMS actuator [13]. On the other hand, DRIE process optimization for hole arrays was primarily done at the 10 micronscale to fabricate through-silicon-via, and aspect ratios of up to 26 have been achieved for 15-µm diameter hole arrays [8, 14, 15]. In order to increase the density of vias, DRIE process optimization was carried out on 1 micronscale and aspect ratios of up to 17 have been achieved for 2 and 3-µm diameter hole arrays [16, 17]. However, the cross-sectional area of the hole array diminishes as the aspect ratio increases, resulting in a bottom that is less than half of the top.

<sup>&</sup>lt;sup>1</sup> Department of Mechanical Engineering, Korea Advanced Institute of Science and Technology, Daejeon, South Korea Full list of author information is available at the end of the article

<sup>\*</sup>Correspondence: jungchullee@kaist.ac.kr

In this letter, we introduce an optimized DRIE process for fabricating microscale high aspect ratio hole arrays. Two different optimization strategies are employed to improve the etch profile of microscale hole arrays. One is to promote bottom etching and the other is to minimize the undercut. Etch parameters are optimized for the former, while gas flow rates are optimized for the latter. By combining each optimization result, high aspect ratio microscale hole arrays with a minimized area reduction ratio are successfully fabricated.

## **Optimization parameters**

Paths of the ions and free radicals in the DRIE process are impeded due to the limited area to be etched in the microscale hole array. Furthermore, as the aspect ratio increases, the number of ions and free radicals reaching at the bottom decreases, reducing etch at the bottom of the structure. Due to these effects, the cross-sectional area keeps shrinking toward the bottom of the microscale hole array, eventually becoming self-limited as shown in Fig. 1a and b. This is the most important factor influencing the deterioration of the profile of the high aspect ratio hole array. In order to promote bottom etching, bias voltage and inductively coupled plasma (ICP) power of the etch step are selected as parameters to optimize. The kinetic energy of the ions increases with bias voltage, and the density of the ions and free radicals increases with ICP power [7]. With these effects, the bombardment of ions and free radicals at the bottom is promoted, allowing the profile of the high aspect ratio hole array to be improved.

The upper part of the high aspect ratio hole array is continuously exposed to ions and free radicals as the number of DRIE cycles increases, resulting in undercuts. Due to this, the area of the top of the high aspect ratio

hole array is widened, so it is important to minimize the undercut for improving the profile. In order to minimize the undercut, octafluorocyclobutane ( $C_4F_8$ ) gas flow of passivation step and sulfur hexafluoride (SF<sub>6</sub>) gas flow of the depassivation step are selected as parameters to optimize. An increase in passivation polymer by  $C_4F_8$  gas flow and a reduction in etching of the passivation polymer by SF<sub>6</sub> gas flow are both effective to improve the sidewall protection at the top of the hole array, hence undercut can be reduced.

#### Materials and methods

For high aspect ratio hole array etching, thermal oxides with an etch selectivity of 100:1 in a microscale hole array are selected as an etch mask. On a (100) single crystal silicon wafer, 1  $\mu m$  of thermal oxide is grown by wet oxidation to be able to withstand the etch process sufficiently when etched up to 30  $\mu m$ . Then, patterns with a characteristic dimension ranging from 700 nm to 1.9  $\mu m$  are patterned with an I-line stepper (wavelength = 365 nm), and the patterns are transferred to thermal oxides through RIE process to fabricate etch masks. The photoresist cannot be used as an etch mask for the DRIE process because the photoresist utilized in the I-line stepper has an 800 nm thickness and the etch selectivity in the microscale pattern is as low as 15:1.

Parametric studies are carried out by modifying only one parameter at a time in the standard DRIE recipe as shown in Table 1. The samples are cleaved after each DRIE process, and the cross-sectional profiles are inspected using a scanning electron microscope (SEM). Guided trenches, which allow cracks to form along the trench during cleaving, are placed at both ends of the hole array center in line with the crystal direction, allowing the cross-section to pass through the center of the

Fig. 1 a Schematic showing the cross-section of the trench and hole array under the same DRIE process. **b** Schematic showing the different numbers of ions and free radicals reaching the bottom due to the loading effect during the DRIE process

hole. Furthermore, during cross-sectional SEM inspection, tilting is used to determine whether the cross-section passed through the center of the hole. Because the bottom of the microscale high aspect ratio pattern is narrower than the top, an area reduction ratio  $(1-(D_B/D_T)^2)^2$  or  $1-(W_B/W_T)$ ,  $D_T$ ,  $D_B$ ,  $W_T$  and  $W_B$  are depicted in Fig. 1) is proposed to quantify the nonuniform etch profiles. Each fabrication results are analyzed through the area reduction ratio and etch depth. Finally, each optimized parameter is combined to make an optimized recipe for fabricating a microscale hole array.

#### **Results and discussion**

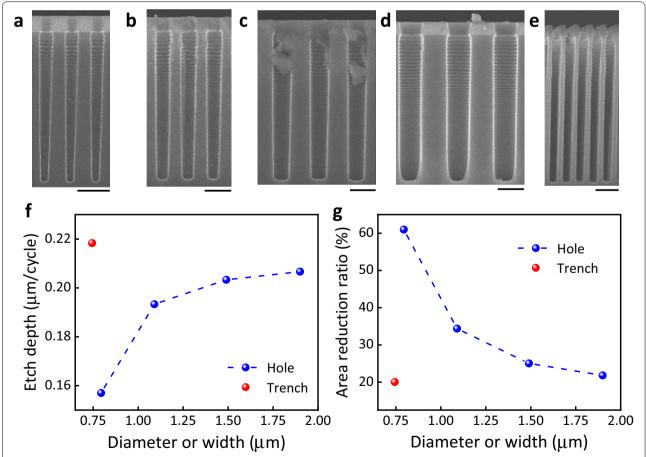

Hole arrays and trench are fabricated to compare the loading effect. Hole arrays with diameters ranging from 0.79 to 1.90  $\mu$ m (Fig. 2a–d) and trench with width of 0.74  $\mu$ m (Fig. 2e) are fabricated by etching 60 cycles using the standard DRIE recipe in Table 1. For 0.79  $\mu$ m, 1.09  $\mu$ m, 1.49  $\mu$ m, and 1.90  $\mu$ m-diameter hole arrays, the areal number densities, which represent the

number of patterns per unit area, are  $4.8 \times 10^5 \text{ mm}^{-2}$ ,  $2.7 \times 10^5 \text{ mm}^{-2}$ ,  $1.2 \times 10^5 \text{ mm}^{-2}$ , and  $8 \times 10^4 \text{ mm}^{-2}$ , respectively. For a trench with a width of  $0.74 \, \mu \text{m}$ , the areal number density is  $8.8 \times 10^2 \text{ mm}^{-2}$ . As shown in Fig. 2f and g, the etch depth decreases as the hole diameter decreases, while the area reduction ratio increases. Furthermore, as the diameter decreases, the loading effect becomes more significant. Compared to the hole array having the same diameter as the width of the trench, the trench is more beneficial in both etch depth and area reduction ratio due to the large area to be etched. Therefore, optimizing the DRIE parameters for fabricating high aspect ratio hole arrays is required.

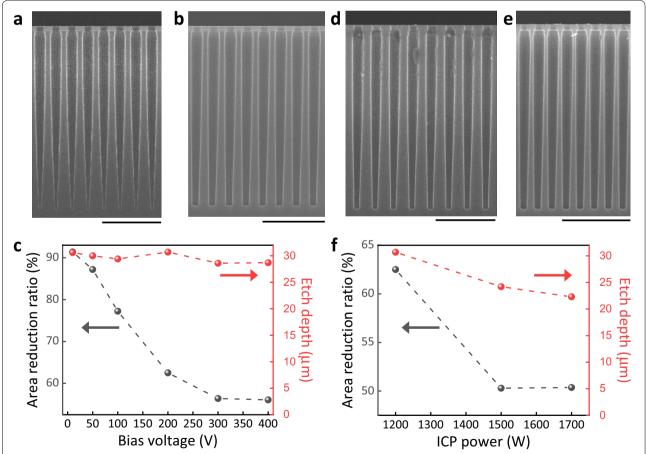

In order to promote bottom etching of the high aspect ratio hole array, parametric studies are carried out on the bias voltage and ICP power of the etch step. First, the change in the cross-section of a 1.6-µm diameter hole array is investigated while increasing the bias voltage from 10 to 400 V at 200 cycles. The areal number

**Fig. 2** SEM cross-sectional images of hole arrays with various diameters **a** 0.79 μm, **b** 1.09 μm, **c** 1.49 μm and **d** 1.90 μm) after 60 DRIE cycles with the standard DRIE recipe. SEM cross-sectional image of trench array with a width of **e** 0.74 μm. **f** Etch depth and **g** area reduction ratio as a function of hole diameter or trench width. All scale bars are 2 μm

density of the 1.6-µm diameter hole array ranges from  $1.3 \times 10^5$  mm<sup>-2</sup> to  $1.7 \times 10^5$  mm<sup>-2</sup>. Cross-sectional SEM images of hole arrays etched at bias voltage of 10 V and 300 V, respectively, are shown in Fig. 3a and b. The etch depth and area reduction ratio are compared as shown in Fig. 3c. Although the etch depth does not change significantly as the bias voltage increases, the area reduction ratio tends to decrease. The kinetic energy of the ions rises as the bias voltage increases, allowing more ions to reach the bottom and thereby accelerating the etching. As shown in Fig. 3b, the area reduction ratio achieved 56% at a bias voltage of 300 V, but not further improved at 400 V. Therefore, a bias voltage of 300 V is selected as the optimal value. Following that, the effect of increasing ICP power on improving profile, which promotes etching of the bottom area due to increased ion density, is investigated. However, ions do not relax in micro and sub-micron hole array with high aspect ratio, causing the sidewall of silicon to be charged and reducing the ion flux [18]. As a result, the depth that ions can reach decreases, resulting in a reduction in etch depth. Despite the fact that the etch depth decreases as the ICP power increases, the change in cross-section of a 1.5-µm diameter hole array is investigated while increasing the ICP power from 1200 to 1700 W with a bias voltage of 200 V at 200 cycles. The areal number density of the 1.6-µm diameter hole array ranges from  $1.1 \times 10^5$  mm<sup>-2</sup> to  $2.2 \times 10^5$  mm<sup>-2</sup>. Cross-sectional SEM images of hole arrays etched at ICP power of 1200 W and 1500 W, respectively, are shown in Fig. 3d and e. The etch depth and area reduction ratio are compared as shown in Fig. 3f. The area reduction ratio decreases as the ICP power increases due to the increased ion density, and the etch depth decreased as well, as expected. As shown in Fig. 3e, the area reduction ratio is achieved 50% at an ICP power of 1500 W, but not further improved at 1700 W. Therefore, 1500 W is chosen as the optimal value.

**Fig. 3** SEM cross-sectional images of 1.6 μm-diameter hole arrays etched 200 cycles by modified DRIE recipe with bias voltage of **a** 10 V and **b** 300 V. **c** Area reduction ratio and etch depth as a function of bias voltage. SEM cross-sectional images of 1.5-μm diameter hole arrays etched 200 cycles by modified DRIE recipe with ICP power of **d** 1200 W and **e** 1500 W. **f** Area reduction ratio and etch depth as a function of ICP power. All scale bars are 10 μm

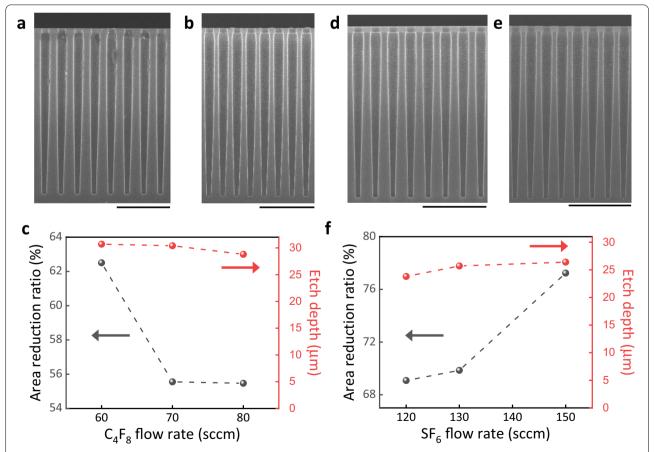

In order to minimize the undercut of the high aspect ratio hole array, parametric studies are carried out on the C<sub>4</sub>F<sub>8</sub> gas flow of passivation step and SF<sub>6</sub> gas flow of depassivation step. First, the effect of increasing C<sub>4</sub>F<sub>8</sub> gas flow, which enhance the passivation of the sidewall, is investigated. The change in cross-section of a 1.6µm diameter hole array is investigated while increasing the C<sub>4</sub>F<sub>8</sub> gas flow from 60 to 80 sccm with a bias voltage of 200 V at 200 cycles. The areal number density of the 1.6- $\mu$ m diameter hole array ranges from  $1.1 \times 10^5$  $\mathrm{mm^{-2}}$  to  $1.6 \times 10^5$   $\mathrm{mm^{-2}}$ . Cross-sectional SEM images of hole arrays etched at C<sub>4</sub>F<sub>8</sub> gas flow of 60 sccm and 70 sccm, respectively, are shown in Fig. 4a and b. The etch depth and area reduction ratio are compared as shown in Fig. 4c. The area reduction ratio decreases as the C<sub>4</sub>F<sub>8</sub> gas flow increases, and the etch depth decreases slightly. Because the width of the widest part of the top decrease from 1.66 (Fig. 4a) to 1.55 µm (Fig. 4b) as the passivation polymer increases, the area reduction ratio decreases. As shown in Fig. 4b, the area reduction ratio achieved 55% at a C<sub>4</sub>F<sub>8</sub> gas flow of 70 sccm, but not further improved at 80 sccm. Therefore, a  $C_4F_8$  gas flow of 70 sccm is selected as the optimal value. Although sidewall protection is improved due to the increased passivation polymer, the etch depth tends to decrease slightly, which is thought to be caused by residual polymer at the bottom due to the thick passivation layer. Following that, the effect of decreasing SF<sub>6</sub> gas flow, which reduce the etching of the sidewall passivation polymer, is investigated. The change in cross-section of a 1.6-um diameter hole array is investigated while increasing the SF<sub>6</sub> gas flow from 120 sccm to 150 sccm with a bias voltage of 100 V at 200 cycles. The areal number density of the 1.6-µm diameter hole array ranges from  $1.2 \times 10^5$  mm<sup>-2</sup> to  $1.6 \times 10^5$  mm<sup>-2</sup>. Cross-sectional SEM images of hole arrays etched at SF<sub>6</sub> gas flow of 120 sccm and 150 sccm, respectively, are shown in Fig. 4d and e. The etch depth and area reduction ratio are compared as shown in Fig. 4f. The area reduction ratio decreases as the SF<sub>6</sub> gas flow decreases, and the etch depth decreases slightly. Because the width of the

**Fig. 4** SEM cross-sectional images of 1.6  $\mu$ m-diameter hole arrays etched 200 cycles by modified DRIE recipe with C<sub>4</sub>F<sub>8</sub> gas flow rate of **a** 60 sccm and **b** 70 sccm. **c** Area reduction ratio and etch depth as a function of C<sub>4</sub>F<sub>8</sub> gas flow rate. SEM cross-sectional images of 1.6  $\mu$ m-diameter hole arrays etched 200 cycles by modified DRIE recipe with SF<sub>6</sub> gas flow rate of **d** 120 sccm and **e** 150 sccm. **f** Area reduction ratio and etch depth as a function of SF<sub>6</sub> gas flow rate. All scale bars are 10  $\mu$ m

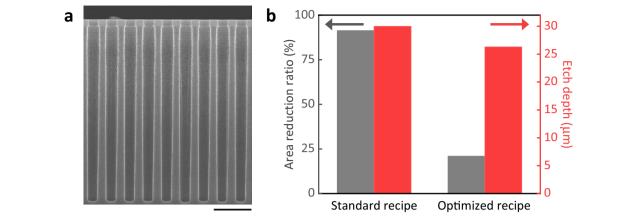

**Fig. 5** a SEM cross-sectional images of 1.3 µm-diameter hole arrays etched 200 cycles by optimized DRIE recipe. **b** Area reduction ratio and etch depth depending on the recipe used in the DRIE process. Scale bar is 5 µm

Table 1 Standard DRIE recipe

|                                      | Passivation | Depassivation | Etch |

|--------------------------------------|-------------|---------------|------|

| Process time (sec)                   | 2.0         | 2.0           | 1.5  |

| ICP power (W)                        | 1500        | 1500          | 1200 |

| Bias voltage (V)                     | 10          | 400           | 10   |

| Pressure (mTorr)                     | 25          | 25            | 20   |

| C <sub>4</sub> F <sub>8</sub> (sccm) | 60          | 0             | 0    |

| SF <sub>6</sub> (sccm)               | 0           | 150           | 100  |

| Ar (sccm)                            | 30          | 30            | 30   |

Table 2 Optimized DRIE recipe

|                                      | Passivation | Depassivation | Etch |  |

|--------------------------------------|-------------|---------------|------|--|

| Process time (sec)                   | 2.0         | 2.0           | 1.5  |  |

| ICP power (W)                        | 1500        | 1500          | 1500 |  |

| Bias voltage (V)                     | 10          | 400           | 300  |  |

| Pressure (mTorr)                     | 25          | 25            | 20   |  |

| C <sub>4</sub> F <sub>8</sub> (sccm) | 70          | 0             | 0    |  |

| SF <sub>6</sub> (sccm)               | 0           | 120           | 100  |  |

| Ar (sccm)                            | 30          | 30            | 30   |  |

widest part of the top decrease from 1.66 (Fig. 4d) to 1.57  $\mu m$  (Fig. 4e) as the etch gas of the polymer decreases, the area reduction ratio decreases. As shown in Fig. 4e, the area reduction ratio achieved 69% at a SF<sub>6</sub> gas flow of 120 sccm. The area reduction ratio reduces as the etching gas flow rate decreases, but the etch depth also decreases due to the unetched polymer at the bottom. The improvement of the area reduction ratio will be insignificant when the SF<sub>6</sub> gas flow rate is further reduced, while the etch depth will be reduced. Therefore, a SF<sub>6</sub> gas flow of 120 sccm is selected.

The optimized DRIE recipe in Table 2, combining the parameters optimized for each step, is applied to run the 200 cycle DRIE process. The cross-sectional profile of the 1.3  $\mu m$ -diameter hole array with area number density of  $1.8\times 10^5~mm^{-2}$  is enhanced the most by obtaining an aspect ratio of 20 and an area reduction ratio of 21% as shown in Fig. 5a. Comparing this result with the 1.6  $\mu m$ -diameter hole array etched by 200 cycles using the standard DRIE recipe, the area reduction ratio is improved by 70% as shown in Table 3, despite the smaller diameter. Furthermore, as can be observed from the parametric study results, the modest decrease in etch depth

**Table 3** Comparison of the area reduction ratio for a 1.6 μm-diameter hole array etched with a standard DRIE recipe and a 1.3 μm-diameter hole array etched with an optimized recipe

|                          | Standard DRIE<br>recipe (A <sub>1</sub> ) | Optimized DRIE recipe (A <sub>2</sub> ) | Improvement (A <sub>1</sub> -A <sub>2</sub> ) |

|--------------------------|-------------------------------------------|-----------------------------------------|-----------------------------------------------|

| Area reduction ratio (%) | 91                                        | 21                                      | 70                                            |

to 26.3  $\mu m$  (Fig. 5b) is an effect of the increased ICP power.

#### **Conclusion**

In this letter, we introduce an optimization for the fabrication of high aspect ratio microscale hole arrays. To improve the area reduction ratio of the high aspect ratio hole array, two approaches are used. One is to promote bottom etching and the other is to reduce undercuts. The former is more effective in terms of improving the area reduction ratio. By optimizing the bias voltage and ICP power of the etch step, the area reduction ratios are reduced by 35% and 12%, respectively. Furthermore, the

latter improves the area reduction ratio to some degree. By optimizing the  $C_4F_8$  gas flow of the passivation step and the  $SF_6$  gas flow of the depassivation step, the area reduction ratios are reduced by 7% and 8%, respectively, due to modest reduction of the undercut. Finally, a 1.3  $\mu$ m-diameter hole array with an aspect ratio of 20 is fabricated by DRIE process with a recipe combining each optimized parameter, and an area reduction ratio of 21% is achieved. The optimized DRIE process is well suited for fabricating microscale hole arrays, and based on the parameters optimized in this study, it is expected that hole arrays with an aspect ratio higher than 20 can be fabricated once the DRIE cycle is increased.

#### Acknowledgements

Authors are grateful to the National Research Foundation of Korea for the funds received.

#### **Author contributions**

TK optimized the DRIE process and wrote the manuscript. JL supervised the research and the manuscript. Both authors read and approved the final manuscript.

#### **Funding**

This research was supported by Basic Science Research Program through the National Research Foundation of Korea(NRF) funded by the Ministry of Education (NRF-2020R1A2C3004885 and NRF-2020R1A4A2002728).

#### Availability of data and materials

The datasets used and/or analysed during the current study are available from the corresponding author on reasonable request.

#### **Declarations**

### Consent for publication

$\label{prop:equation:consent} \mbox{Authors consent the SpringerOpen license agreement to publish the article.}$

#### Competing interests

The authors declare that they have no competing interests.

#### **Author details**

<sup>1</sup>Department of Mechanical Engineering, Korea Advanced Institute of Science and Technology, Daejeon, South Korea. <sup>2</sup>Center for Extreme Thermal Physics and Manufacturing, Korea Advanced Institute of Science and Technology, Daejeon, South Korea.

Received: 15 July 2022 Accepted: 28 August 2022 Published online: 09 September 2022

#### References

- Park JS, Kang D-H, Kwak SM, Kim TS, Park JH, Kim TG, Baek S-H, Lee BC (2020) Low-temperature smoothing method of scalloped DRIE trench by post-dry etching process based on SF<sub>6</sub> plasma. Micro Nano Syst Lett 8(1):1–8

- Cho D-ID, Hong S, Lee M, Kim T (2015) A review of silicon microfabricated ion traps for quantum information processing. Micro Nano Syst Lett 3(1):1–12

- Kamto A, Liu Y, Schaper L, Burkett SL (2009) Reliability study of through-silicon via (TSV) copper filled interconnects. Thin Solid Films 518(5):1614–1619

- Richter K, Viehweger K, He J, Bartha J-W (2009) Creation of vias with optimized profile for 3-D through silicon interconnects (TSV). Plasma Process Polym 6(S1):193–197

- Chen B, Miao J (2007) Influence of deep RIE tolerances on comb-drive actuator performance. J Phys D Appl Phys 40(4):970–976

- Kim M, Park J-H, Jeon J-A, Yoo B-W, Park IH, Kim Y-K (2009) High fill-factor micromirror array using a self-aligned vertical comb drive actuator with two rotational axes. J Micromech Microeng 19(3):035014

- Shi Z, Jefimovs K, Romano L, Stampanoni M (2020) Towards the fabrication of high-aspect-ratio silicon gratings by deep reactive ion etching. Micromachines 11(9):864

- 8. Tang Y, Sandoughsaz A, Owen KJ, Najafi K (2018) Ultra deep reactive ion etching of high aspect-ratio and thick silicon using a ramped-parameter process. J. Microelectromechanical Syst. 27(4):686–697

- Wu B, Kumar A, Pamarthy S (2010) High aspect ratio silicon etch: a review. J Appl Phys 108(5):051101

- Parasuraman J, Summanwar A, Marty F, Basset P, Angelescu DE, Bourouina T (2014) Deep reactive ion etching of sub-micrometer trenches with ultra high aspect ratio. Microelectron Eng 113:35–39

- Finnegan PS, Hollowell AE, Arrington CL, Dagel AL (2019) High aspect ratio anisotropic silicon etching for X-ray phase contrast imaging grating fabrication. Mater Sci Semicond Process 92:80–85

- Hollowell AE, Arrington CL, Finnegan P, Musick K, Resnick P, Volk S, Dagel AL (2019) Double sided grating fabrication for high energy X-ray phase contrast imaging. Mater Sci Semicond Process 92:86–90

- Wang J (2012) Silicon-on-insulator out-of-plane electrostatic actuator with in situ capacitive position sensing. J Micro Nanolithogr MEMS MOEMS 11(3):033006

- Song C, Wang Z, Chen Q, Cai J, Liu L (2008) High aspect ratio copper through-silicon-vias for 3D integration. Microelectron Eng 85(10):1952–1956

- Ham Y-H, Kim D-P, Park K-S, Jeong Y-S, Yun H-J, Baek K-H, Kwon K-H, Lee K, Do L-M (2011) Dual etch processes of via and metal paste filling for through silicon via process. Thin Solid Films 519(20):6727–6731

- Civale Y, Armini S, Philipsen H, Redolfi A, Velenis D, Croes K, Heylen N, El-Mekki Z, Vandersmissen K, Beyer G, Swinnen B, Beyne E (2012) Enhanced barrier seed metallization for integration of high-density high aspectratio copper-filled 3D through-silicon via interconnects. In: 2012 IEEE 62nd electronic components and technology conference. pp 822–826

- 17. Zhang D, Smith D, Kumarapuram G, Giridharan R, Kakita S, Rabie MA, Feng P, Edmundson H, England L (2015) Process development and optimization for 3 µm high aspect ratio via-middle through-silicon vias at wafer level. IEEE Trans Semicond Manuf 28(4):454–460

- Imai S-i (2008) Bias power dependence of reactive ion etching lag in contact hole etching using inductively coupled fluorocarbon plasma. J Vac Sci Technol B Nanotechnol Microelectron 26(6):2008–2012

#### **Publisher's Note**

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

# Submit your manuscript to a SpringerOpen journal and benefit from:

- ► Convenient online submission

- ► Rigorous peer review

- ▶ Open access: articles freely available online

- ► High visibility within the field

- ▶ Retaining the copyright to your article

Submit your next manuscript at ▶ springeropen.com